Get the free Dynamic Reconfiguration of Fpga Nodes in a Distributed Computing System: a Prelimina...

Get, Create, Make and Sign dynamic reconfiguration of fpga

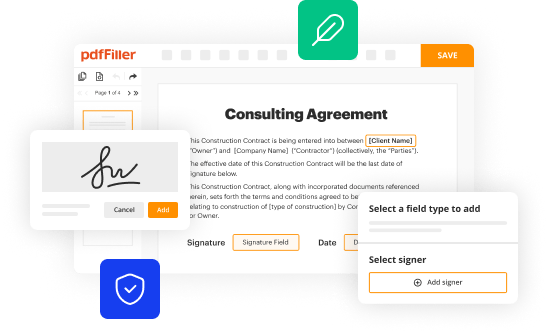

Editing dynamic reconfiguration of fpga online

Uncompromising security for your PDF editing and eSignature needs

How to fill out dynamic reconfiguration of fpga

How to fill out dynamic reconfiguration of fpga

Who needs dynamic reconfiguration of fpga?

Dynamic reconfiguration of FPGA form: A comprehensive guide

Understanding dynamic reconfiguration in FPGAs

Dynamic reconfiguration refers to the ability of Field-Programmable Gate Arrays (FPGAs) to change their configuration while remaining operational. This technology allows designers to update the logic and functionality of FPGAs during execution without taking the system offline, leading to increased system flexibility and adaptability. The importance of this capability cannot be overstated, as it enables FPGAs to efficiently meet varying application demands and operational conditions.

The benefits of dynamic reconfiguration are significant for a wide range of applications, leading to reduced downtime and more efficient resource utilization. By adjusting the configuration only as needed, users can save power and cost, especially in environments where resources are limited or where systems must remain operational 24/7.

Use cases and applications

Dynamic reconfiguration plays a crucial role in various sectors, including:

Key components of FPGA dynamic reconfiguration

Understanding the architecture of FPGAs is vital for grasping how dynamic reconfiguration operates. FPGAs consist of configurable logic blocks (CLBs), look-up tables (LUTs), flip-flops, and a network of programmable interconnects. Each of these components plays a role in the reconfiguration process. The design and organization of these elements directly influence the speed and efficiency of the dynamic reconfiguration capabilities.

Different types of configuration memory further impact how dynamic reconfiguration is managed. The popular types include SRAM, Flash, and EEPROM, each with unique traits:

Techniques for implementing dynamic reconfiguration

Implementing dynamic reconfiguration can be achieved through several techniques, notably partial and full reconfiguration. Partial reconfiguration allows certain sections of the FPGA to be reconfigured while others continue to function, minimizing downtime and maximizing efficiency. To implement this, designers typically follow a structured approach, which includes defining the regions to be reconfigured and verifying their configurations through specialized design tools.

Full reconfiguration, on the other hand, involves a complete reset and reconfiguration of the FPGA. This method should be utilized when changes necessary warrant a full overhaul of the system or when encountering critical failures. Best practices suggest running simulations and maintaining backups of the previous configurations before initiating a full reconfiguration.

To effectively manage dynamic reconfiguration, a systematic design flow must be adhered to. Utilizing appropriate toolchains is crucial for creating optimal configurations; methodologies might differ based on the specific use case but should always lead from specification through design, verification, and ultimately to reconfiguration.

Challenges in dynamic reconfiguration

Despite its benefits, dynamic reconfiguration comes with its challenges. Addressing latency is critical as reconfiguration time can impact system responsiveness. Techniques such as employing faster memory options and optimizing the reconfiguration process can help reduce latency, ensuring that changes occur seamlessly.

Reliability is another concern during reconfigurations. Strategies include implementing watchdog timers that can reset components in case of failure and using diverse redundancy to maintain operational integrity. Special care must also be taken to manage resource constraints, especially in environments with limited FPGA resources. Optimization tips include minimizing resource usage through efficient coding practices and reusing logic components wherever possible.

Interfacing with other components

Interfacing FPGAs with microcontrollers and System on Chips (SoCs) is vital for harnessing the full benefits of dynamic reconfiguration. Understanding communication protocols, such as SPI, I2C, and UART, will facilitate efficient communication between components and ensure that configuration changes can be communicated effectively.

Design considerations when integrating FPGAs with microcontrollers include selecting the right speed and data width, which could significantly affect performance. Additionally, utilizing Intellectual Property (IP) cores can greatly expand the functionality available for dynamic reconfiguration. These cores often provide tried-and-tested design blocks that alleviate the need for developing components from scratch, offering a streamlined solution.

Examples of useful IP cores for dynamic reconfiguration include high-speed serialization cores for communication improvements and video processing cores, which aid in multimedia applications.

Tools and software for dynamic reconfiguration

The success of dynamic reconfiguration relies heavily on utilizing effective design environments. Popular FPGA design tools like Xilinx Vivado and Intel Quartus provide vast resources for debugging and development, helping engineers streamline the design process and incorporate dynamic reconfiguration with ease.

Moreover, the importance of simulation cannot be overstated. Utilizing simulation and testing tools allows designers to validate configurations before deployment, minimizing the occurrence of errors and ensuring system reliability. Suggested tools for simulation include ModelSim and Vivado Simulator, which provide comprehensive environments for testing the behaviors of FPGA designs.

Real-world examples and case studies

Examining real-world applications can provide insight into the practical benefits of dynamic reconfiguration. For instance, in the automotive sector, dynamic reconfiguration has enabled the development of advanced driver-assistance systems (ADAS). Such systems can update functionalities based on real-time data, ensuring higher safety and efficiency.

Another industry example lies in telecommunications. A case study showed how a telecommunications company successfully used dynamic reconfiguration to manage bandwidth allocations dynamically, thereby optimizing service delivery in dense urban environments.

Innovations in various sectors have been significantly advanced by the capabilities offered by dynamic reconfiguration, illustrating its importance for the future of technology.

Future of FPGA dynamic reconfiguration

As technology progresses, emerging trends in FPGA technology, such as AI acceleration and edge computing, hint at the future trajectory of dynamic reconfiguration practices. These trends suggest that the demand for adaptable and optimized FPGA solutions will increase, driven by the growth of data-intensive applications across all sectors.

Predictions for the future of dynamic reconfiguration include advancements in algorithm efficiency and the development of even more flexible FPGA configurations. As the technology matures, we may also see the emergence of new protocols and methodologies that further enhance reconfiguration processes, ensuring that FPGAs can continue to meet evolving demands.

Interactive tools and resources on FPGA dynamic reconfiguration

To facilitate exploration and learning about dynamic reconfiguration, various interactive design tools are available. These tools allow users to simulate configurations dynamically and can provide instant feedback on design modifications.

Additionally, downloadable templates tailored for dynamic reconfiguration projects can serve as beneficial starting points for engineers seeking to implement their own designs. These resources will empower users by providing structured frameworks to streamline their projects.

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

How do I modify my dynamic reconfiguration of fpga in Gmail?

Can I create an eSignature for the dynamic reconfiguration of fpga in Gmail?

Can I edit dynamic reconfiguration of fpga on an Android device?

What is dynamic reconfiguration of FPGA?

Who is required to file dynamic reconfiguration of FPGA?

How to fill out dynamic reconfiguration of FPGA?

What is the purpose of dynamic reconfiguration of FPGA?

What information must be reported on dynamic reconfiguration of FPGA?

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.