Get the free Verilog code compiles but why won't the simulation run?

Get, Create, Make and Sign verilog code compiles but

How to edit verilog code compiles but online

Uncompromising security for your PDF editing and eSignature needs

How to fill out verilog code compiles but

How to fill out verilog code compiles but

Who needs verilog code compiles but?

Verilog code compiles but form

Understanding Verilog compilation

Verilog is a powerful hardware description language (HDL) used extensively in digital design and simulation for integrated circuits. It allows designers to model electronic systems at different levels of abstraction ranging from high-level algorithmic descriptions to low-level gate-level specifications. Its importance is highlighted by its widespread adoption in industries involving FPGA and ASIC design.

The process of compiling Verilog code is critical for transforming written design specifications into a format suitable for simulation and synthesis. This compilation process ensures that the code adheres to the syntax and semantic rules established for Verilog, ultimately enabling designers to validate their designs.

Common issues with Verilog compilation

Even an otherwise well-written Verilog code can face compilation issues. Being able to identify compilation errors effectively is essential for a smooth workflow. Errors can be classified into three main types: syntax errors, semantic errors, and runtime errors. Syntax errors are typically straightforward, deriving from incorrect format or missing keywords. Semantic errors present more complexity as they involve incorrect logic or functionality despite valid syntax. Runtime errors arise during the execution of compiled code, often due to unforeseen conditions.

To combat these issues, several tools are available that can assist with error identification. Integrated development environments (IDEs) like ModelSim and Vivado provide comprehensive logging and debugging features, paving the way for efficient troubleshooting.

Practical examples: Verilog code scenarios

To understand how Verilog code compiles, it’s important to examine both basic and advanced examples. A simple Verilog module can illustrate the basic structure necessary for compilation. Consider a simple AND gate module, which serves as an excellent starting point for understanding module creation and how code compilation processes function.

The code compilation for such a module typically follows these steps: write the module, compile within the IDE, simulate to verify functionality, and finally, ensure comments and documentation are thorough.

Advanced design example

In more complex designs, utilizing conditional compilation can significantly streamline the workflow. For instance, parameterized modules enhance versatility, allowing designers to adjust dimensions or performance characteristics by changing just a few parameters. Such practices not only improve code manageability but also reduce compilation time.

Real-world example: A testbench

Creating a testbench is essential for functional verification of Verilog modules. Testbenches provide a controlled environment in which you can simulate various inputs and check the corresponding outputs, confirming the functionality of the design before final deployment. The compilation process for a testbench follows similar principles—introducing isolation from other modules while maintaining clarity and structure.

Interactive tools for managing Verilog code

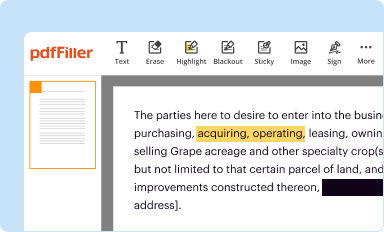

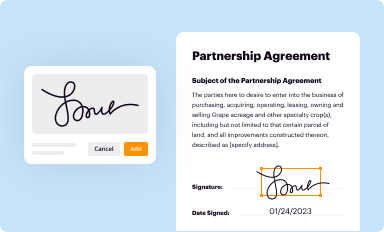

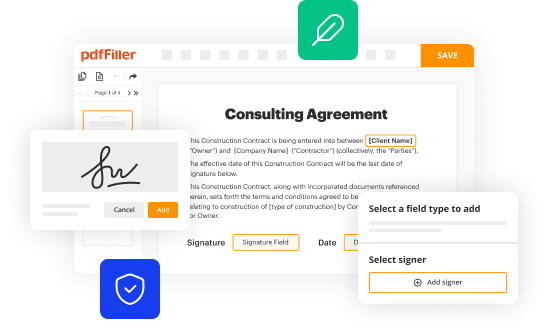

As Verilog code becomes integral to larger collaborative projects, tools that aid in documentation and file management become increasingly vital. pdfFiller offers features that empower teams to manage Verilog-related documents with efficiency. These include the ability to edit, sign, and share essential documents securely, directly from the cloud.

Using pdfFiller, teams can create a streamlined process for managing project documentation. This begins with editing documents such as specification sheets, project plans, and test results, ensuring all members remain on the same page throughout the project lifecycle.

Enhancing your workspace for Verilog compilation

Setting up an effective development environment is crucial for optimizing Verilog compilation. Recommended IDEs such as Active-HDL, Quartus Prime, and Vivado offer robust features tailored for Verilog development. Each comes with unique capabilities such as waveform viewers, advanced debugging, and synthesis tools that help streamline the design process.

Additionally, project documentation management is paramount. The importance of maintaining updated and comprehensive documentation cannot be overstated. pdfFiller provides tools for organizing, editing, and distributing project-related documents, ensuring that every team member has access to the most current information.

Conclusion: Streamlining your Verilog workflow

In summary, understanding the nuances of Verilog code compilation is essential for anyone involved in digital design. Familiarity with common issues and practical examples enhances one’s ability to troubleshoot effectively. Incorporating tools like pdfFiller into your workflow not only aids in documentation management but also fosters collaboration within teams, leading to more efficient project execution.

As you continue your exploration of Verilog, consider how adopting best practices in documentation and utilizing cloud-based platforms can elevate your overall development experience.

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

Where do I find verilog code compiles but?

How do I edit verilog code compiles but online?

How do I edit verilog code compiles but on an Android device?

What is verilog code compiles but?

Who is required to file verilog code compiles but?

How to fill out verilog code compiles but?

What is the purpose of verilog code compiles but?

What information must be reported on verilog code compiles but?

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.