Get the free VSIPL++/FPGA Design Methodology - dtic

Show details

This document details a hardware/software co-design methodology for hybrid hardware and software systems, integrating VSIPL++ for software design and a portable hardware design method based on streams,

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign vsiplfpga design methodology

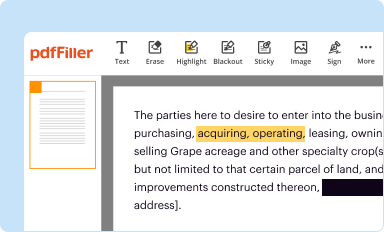

Edit your vsiplfpga design methodology form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

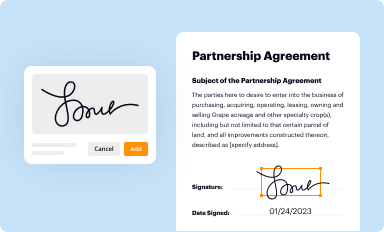

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

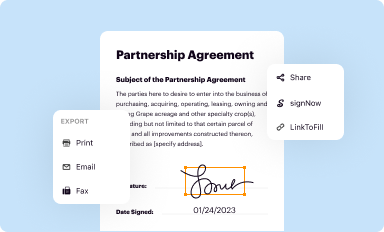

Share your form instantly

Email, fax, or share your vsiplfpga design methodology form via URL. You can also download, print, or export forms to your preferred cloud storage service.

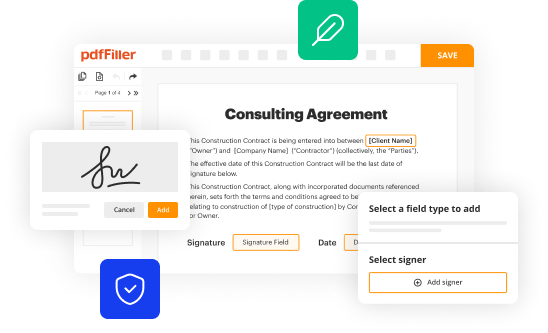

Editing vsiplfpga design methodology online

To use the professional PDF editor, follow these steps:

1

Log in to your account. Start Free Trial and sign up a profile if you don't have one yet.

2

Prepare a file. Use the Add New button to start a new project. Then, using your device, upload your file to the system by importing it from internal mail, the cloud, or adding its URL.

3

Edit vsiplfpga design methodology. Replace text, adding objects, rearranging pages, and more. Then select the Documents tab to combine, divide, lock or unlock the file.

4

Save your file. Select it from your records list. Then, click the right toolbar and select one of the various exporting options: save in numerous formats, download as PDF, email, or cloud.

pdfFiller makes dealing with documents a breeze. Create an account to find out!

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out vsiplfpga design methodology

How to fill out VSIPL++/FPGA Design Methodology

01

Identify the project requirements for your design.

02

Install the necessary software tools for VSIPL++ and FPGA development.

03

Start by creating a new project in your development environment.

04

Define the data flow and algorithms to be implemented using VSIPL++.

05

Map the designed algorithms to hardware resources in your FPGA.

06

Optimize your code for performance and resource utilization.

07

Test the design using simulation tools to ensure functionality.

08

Synthesize the design and generate the configuration file for FPGA.

09

Program the FPGA with the generated configuration file.

10

Validate the final design in a real-world environment.

Who needs VSIPL++/FPGA Design Methodology?

01

Hardware engineers working on FPGA design projects.

02

Software developers looking to implement high-performance computing applications.

03

Researchers developing algorithms that require efficient hardware implementation.

04

Companies involved in digital signal processing or embedded systems.

05

Educational institutions teaching courses related to FPGA design and parallel computing.

Fill

form

: Try Risk Free

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

What is VSIPL++/FPGA Design Methodology?

VSIPL++/FPGA Design Methodology is a structured approach to designing and implementing FPGA (Field Programmable Gate Array) systems using the VSIPL++ (Vector Signal Image Processing Library) framework, which combines high-performance computing with efficient hardware utilization.

Who is required to file VSIPL++/FPGA Design Methodology?

Individuals or teams involved in the design and implementation of FPGA systems using the VSIPL++ framework are required to file under this methodology.

How to fill out VSIPL++/FPGA Design Methodology?

To fill out the VSIPL++/FPGA Design Methodology, practitioners should follow established guidelines that outline project specifics, hardware configurations, software components, and the design process, ensuring all critical aspects of the design are documented.

What is the purpose of VSIPL++/FPGA Design Methodology?

The purpose of VSIPL++/FPGA Design Methodology is to provide a clear framework for efficiently designing FPGA systems, ensuring that all design aspects are documented, promoting best practices, and facilitating easier collaboration and integration.

What information must be reported on VSIPL++/FPGA Design Methodology?

The information that must be reported includes design specifications, system architecture, hardware and software interfaces, performance metrics, testing procedures, and any design trade-offs or considerations that were made during the development process.

Fill out your vsiplfpga design methodology online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Vsiplfpga Design Methodology is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.