Get the free Quick Reference for Verilog HDL - ece ucdavis

Show details

This document serves as a brief summary of the syntax and semantics of the Verilog Hardware Description Language, providing constructs that can be synthesized and including referenced examples.

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign quick reference for verilog

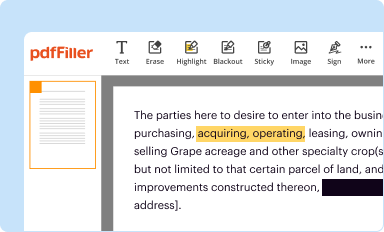

Edit your quick reference for verilog form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

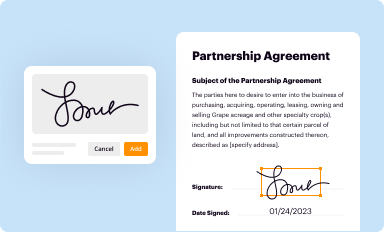

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

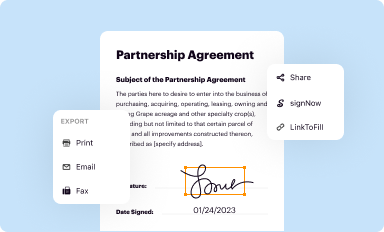

Share your form instantly

Email, fax, or share your quick reference for verilog form via URL. You can also download, print, or export forms to your preferred cloud storage service.

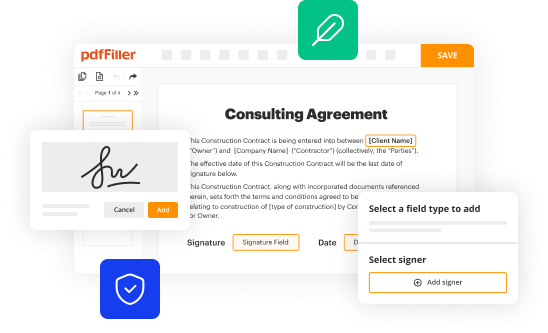

How to edit quick reference for verilog online

Use the instructions below to start using our professional PDF editor:

1

Register the account. Begin by clicking Start Free Trial and create a profile if you are a new user.

2

Prepare a file. Use the Add New button. Then upload your file to the system from your device, importing it from internal mail, the cloud, or by adding its URL.

3

Edit quick reference for verilog. Text may be added and replaced, new objects can be included, pages can be rearranged, watermarks and page numbers can be added, and so on. When you're done editing, click Done and then go to the Documents tab to combine, divide, lock, or unlock the file.

4

Get your file. When you find your file in the docs list, click on its name and choose how you want to save it. To get the PDF, you can save it, send an email with it, or move it to the cloud.

It's easier to work with documents with pdfFiller than you can have believed. Sign up for a free account to view.

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out quick reference for verilog

How to fill out Quick Reference for Verilog HDL

01

Begin by gathering your Verilog HDL project specifications.

02

Identify the key components and functionality needed for your project.

03

Review the standard Verilog syntax and keywords relevant to your design.

04

Create sections for commonly used constructs such as modules, wires, and registers.

05

Outline examples for each construct, providing clear and concise code snippets.

06

Include notes on best practices and common pitfalls to avoid.

07

Ensure that your Quick Reference is organized logically for easy navigation.

08

Review and revise the document for clarity and completeness before finalizing.

Who needs Quick Reference for Verilog HDL?

01

Engineers and designers working on digital circuit design.

02

Students learning Verilog HDL for academic purposes.

03

Professionals needing a quick refresher on Verilog syntax and concepts.

04

Teams collaborating on FPGA and ASIC design projects.

05

Developers looking to streamline their workflow with Verilog code.

Fill

form

: Try Risk Free

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

What is Quick Reference for Verilog HDL?

Quick Reference for Verilog HDL is a concise set of guidelines and syntax reference for using the Verilog Hardware Description Language in the design of digital circuits.

Who is required to file Quick Reference for Verilog HDL?

Individuals involved in digital design and implementation using Verilog HDL, such as hardware engineers and designers, are required to use the Quick Reference.

How to fill out Quick Reference for Verilog HDL?

To fill out Quick Reference for Verilog HDL, one must provide specific details regarding the Verilog code being used, any associated parameters, and ensure that all sections are completed according to the prescribed format.

What is the purpose of Quick Reference for Verilog HDL?

The purpose of Quick Reference for Verilog HDL is to provide a simplified, accessible overview of the language's syntax and functionalities to aid in writing and debugging Verilog code effectively.

What information must be reported on Quick Reference for Verilog HDL?

The information that must be reported includes code snippets, module definitions, data types, control statements, and any relevant comments that clarify the functionality of the code.

Fill out your quick reference for verilog online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Quick Reference For Verilog is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.