Get the free Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs - ...

Show details

This document addresses the main aspects of partial reconfiguration on Xilinx Virtex FPGAs, discussing challenges in design and implementation, particularly regarding signal integrity, global logic,

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign partial configuration design and

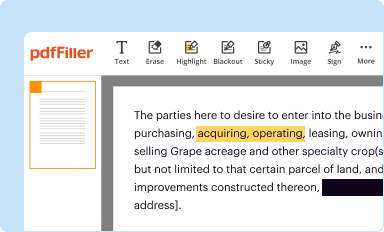

Edit your partial configuration design and form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

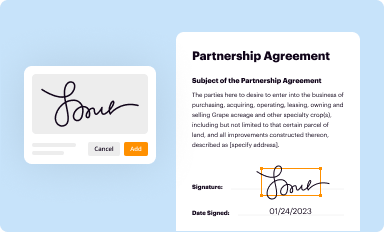

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

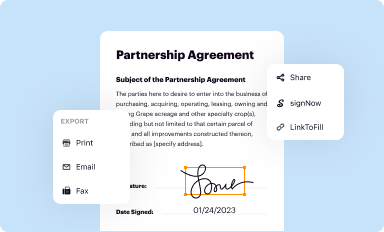

Share your form instantly

Email, fax, or share your partial configuration design and form via URL. You can also download, print, or export forms to your preferred cloud storage service.

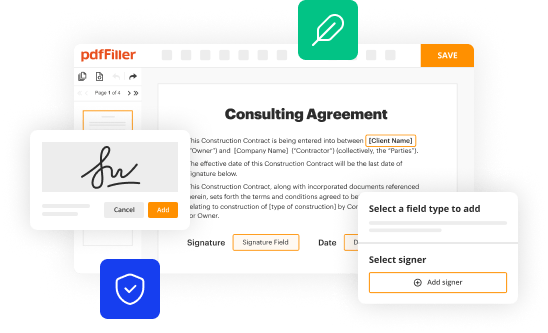

Editing partial configuration design and online

Follow the guidelines below to take advantage of the professional PDF editor:

1

Create an account. Begin by choosing Start Free Trial and, if you are a new user, establish a profile.

2

Prepare a file. Use the Add New button to start a new project. Then, using your device, upload your file to the system by importing it from internal mail, the cloud, or adding its URL.

3

Edit partial configuration design and. Replace text, adding objects, rearranging pages, and more. Then select the Documents tab to combine, divide, lock or unlock the file.

4

Save your file. Select it in the list of your records. Then, move the cursor to the right toolbar and choose one of the available exporting methods: save it in multiple formats, download it as a PDF, send it by email, or store it in the cloud.

It's easier to work with documents with pdfFiller than you could have believed. You may try it out for yourself by signing up for an account.

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out partial configuration design and

How to fill out Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs

01

Identify the application that requires partial reconfiguration.

02

Ensure you have the Xilinx tools installed and updated, including Vivado.

03

Create a new project in Vivado and select the appropriate device (Xilinx Virtex FPGA).

04

Design the static and reconfigurable regions in your HDL code.

05

Model your design using an appropriate partitioning strategy to isolate different functionality.

06

Generate the bitstreams for the static and partial configurations.

07

Test the partial configuration in simulation to ensure functionality.

08

Load the bitstreams onto the FPGA and verify the reconfiguration process.

09

Optimize the design to address timing and resource utilization challenges.

10

Document the process to highlight any issues encountered during implementation.

Who needs Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs?

01

Hardware engineers working on designs utilizing Xilinx Virtex FPGAs.

02

Systems designers implementing adaptive systems requiring runtime reconfiguration.

03

Researchers in FPGA technology exploring dynamic configuration methodologies.

04

Development teams seeking to improve resource utilization and flexibility of their FPGA designs.

Fill

form

: Try Risk Free

People Also Ask about

What is partial reconfiguration in FPGA?

Partial reconfiguration is a design process, which allows a limited, predefined portion of an FPGA to be reconfigured while the remainder of the device continues to operate. Dynamic Partial Reconfiguration is a feature of modern FPGAs that allows runtime modification of an operating FPGA.

How many times can FPGA be reprogrammed?

As many times as a design requires. And there is no specific limit. You might be feeding that FPGAMoreAs many times as a design requires. And there is no specific limit. You might be feeding that FPGA with flash memory for example which might have a limit of its own. But in most cases the FPGA.

What is xilinx Virtex 5?

Xilinx Virtex-5 is a family of high-performance field-programmable gate arrays (FPGAs) designed for advanced logic designs and system-on-chip (SoC) applications.

What is partial reconfiguration of FPGAs?

Partial reconfiguration (PR) allows you to reconfigure a portion of the FPGA dynamically, while the remaining FPGA design continues to function. You can define multiple personas for a particular region in your design, without impacting operation in areas outside this region.

What are the configuration modes of FPGA?

FPGAs can have different configuration modes, such as Master-Serial, Slave-Serial, JTAG (Joint Test Action Group), or Passive Serial. These modes determine how the configuration data is loaded into the FPGA. Configuration Pins: FPGAs have specific pins dedicated to configuration.

What is difference based partial reconfiguration?

The main objective for difference-based partial reconfiguration is allowing small design changes. After the changes are made, the BitGen program is used to produce a bitstream that only programs the differences between the original design and the new one.

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

What is Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs?

Partial Configuration Design involves the ability to change a portion of the FPGA's configuration while the rest of the device remains operational. Challenges include managing design complexity, ensuring timing closure, and handling the interactions between partially and fully reconfigured areas.

Who is required to file Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs?

Design engineers and system architects who are implementing designs using Xilinx Virtex FPGAs and wish to utilize partial reconfiguration capabilities are generally required to document these challenges.

How to fill out Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs?

To fill out the challenges, one should identify and document the specific issues encountered during the design and implementation process, detailing the configurations involved, timing constraints, and any necessary workarounds that were developed.

What is the purpose of Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs?

The purpose is to ensure that all potential difficulties are recognized and addressed during design processes, facilitating more efficient workflows and improving the reliability and performance of the FPGA configuration.

What information must be reported on Partial Configuration Design and Implementation Challenges on Xilinx Virtex FPGAs?

Information that must be reported includes the nature of the design challenge, specific configuration details, timing issues, resource utilization statistics, and the strategies employed to overcome these challenges.

Fill out your partial configuration design and online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Partial Configuration Design And is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.