Get the free compact modeling in verilog a form - eda

Show details

August 13, 2004, Proposed Verilog-A Language Extensions for Compact Modeling Version 9 Describes the changes that should be made to the Verilog-A and Verilog-AMS language definition 1 to better support

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign compact modeling in verilog

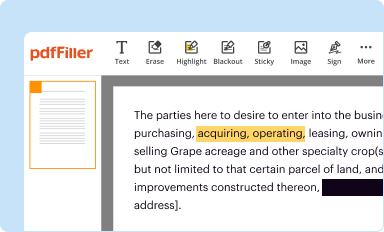

Edit your compact modeling in verilog form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

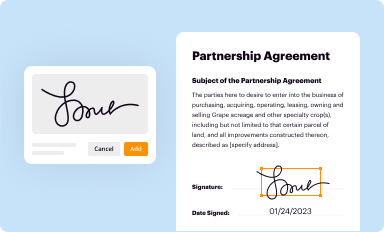

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

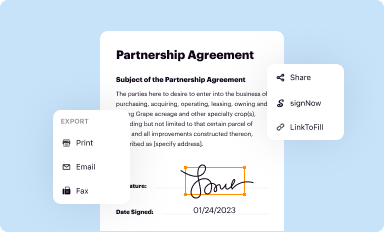

Share your form instantly

Email, fax, or share your compact modeling in verilog form via URL. You can also download, print, or export forms to your preferred cloud storage service.

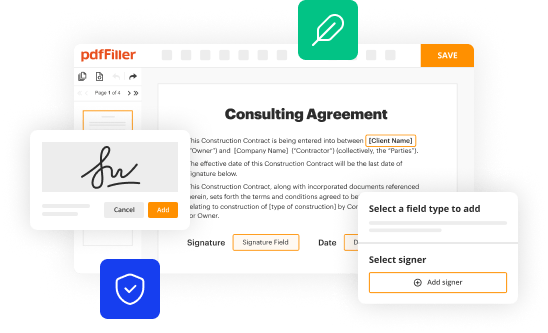

How to edit compact modeling in verilog online

Use the instructions below to start using our professional PDF editor:

1

Log in. Click Start Free Trial and create a profile if necessary.

2

Simply add a document. Select Add New from your Dashboard and import a file into the system by uploading it from your device or importing it via the cloud, online, or internal mail. Then click Begin editing.

3

Edit compact modeling in verilog. Rearrange and rotate pages, add and edit text, and use additional tools. To save changes and return to your Dashboard, click Done. The Documents tab allows you to merge, divide, lock, or unlock files.

4

Save your file. Select it in the list of your records. Then, move the cursor to the right toolbar and choose one of the available exporting methods: save it in multiple formats, download it as a PDF, send it by email, or store it in the cloud.

With pdfFiller, dealing with documents is always straightforward.

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out compact modeling in verilog

How to fill out compact modeling in Verilog:

01

Start by understanding the concept of compact modeling in Verilog. Compact modeling refers to the process of creating simplified mathematical models for electronic devices or circuits. These models are used to simulate and analyze the behavior of the devices or circuits in various applications.

02

Familiarize yourself with the syntax and structure of Verilog, which is a hardware description language used for modeling electronic systems. You will need to know how to define modules, specify inputs and outputs, and describe the behavior of the circuit in Verilog code.

03

Identify the specific device or circuit that you want to model using the compact modeling technique. This could be anything from a basic logic gate to a more complex microprocessor.

04

Determine the level of detail you want to include in the compact model. Depending on your requirements, you can create a highly simplified model that only captures the most essential characteristics of the device or circuit, or you can create a more detailed model that takes into account specific parameters and behaviors.

05

Define the inputs and outputs of the compact model. These are the variables that will be used to interact with the model and simulate its behavior. Make sure to consider the relevant electrical properties and constraints of the device or circuit when defining the inputs and outputs.

06

Implement the behavior of the compact model using Verilog code. This involves specifying the relationships between the inputs and outputs, as well as any internal calculations or logic that need to be performed. You can use a variety of operators, functions, and control structures available in Verilog to describe the desired behavior.

07

Test and validate the compact model by simulating its behavior under different conditions and scenarios. Make sure that the model accurately represents the expected behavior of the actual device or circuit. Adjust and refine the model as necessary based on the simulation results.

Who needs compact modeling in Verilog:

01

Electrical engineers and circuit designers who want to simulate and analyze the behavior of electronic devices or circuits in a virtual environment.

02

Researchers working on the development of new electronic components, who need to understand their behavior and performance before fabrication.

03

Manufacturers and designers of electronic systems, who use compact models to optimize the design of their products and evaluate their performance in different scenarios.

04

Academics and educators who use Verilog and compact modeling as teaching tools for digital circuit design and analysis.

05

Students and hobbyists interested in learning about electronic systems and gaining hands-on experience in circuit simulation and modeling.

Fill

form

: Try Risk Free

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

What is compact modeling in verilog?

Compact modeling in Verilog is a technique used to describe the behavior and characteristics of a digital circuit using a concise and simplified representation in the Verilog hardware description language. It allows designers to simulate and model complex electronic systems in an efficient and systematic manner.

Who is required to file compact modeling in verilog?

The responsibility of filing compact modeling in Verilog lies with the designers, engineers, or researchers who are developing digital circuits and systems using the Verilog hardware description language. They are required to generate and provide a compact model that accurately represents the behavior of the circuit to be used in simulations and optimizations.

How to fill out compact modeling in verilog?

Filling out compact modeling in Verilog involves creating a Verilog module that describes the behavior and characteristics of the digital circuit. This module should define the input and output ports, as well as the internal components and their interconnections. The module should also incorporate any necessary behavioral or timing models to ensure accurate simulation results. Once the Verilog code is written, it can be compiled, simulated, and tested using Verilog compilers and simulators.

What is the purpose of compact modeling in verilog?

The purpose of compact modeling in Verilog is to provide a concise and efficient representation of a digital circuit's behavior. This allows designers to simulate, analyze, optimize, and verify the circuit's functionality without dealing with the complexities of the underlying hardware implementation. Compact modeling enables faster design iterations, improved design quality, and reduced development time and cost.

What information must be reported on compact modeling in verilog?

When reporting compact modeling in Verilog, the information that must be included depends on the specific requirements of the project, circuit, or simulation. Generally, it should include the module's input and output ports, as well as their functionalities and timing characteristics. It should also describe the interconnections between the various components and any behavioral or timing models used. Additionally, any specific design constraints, limitations, or assumptions should be clearly documented.

How can I modify compact modeling in verilog without leaving Google Drive?

Using pdfFiller with Google Docs allows you to create, amend, and sign documents straight from your Google Drive. The add-on turns your compact modeling in verilog into a dynamic fillable form that you can manage and eSign from anywhere.

How can I get compact modeling in verilog?

The premium pdfFiller subscription gives you access to over 25M fillable templates that you can download, fill out, print, and sign. The library has state-specific compact modeling in verilog and other forms. Find the template you need and change it using powerful tools.

How do I make edits in compact modeling in verilog without leaving Chrome?

Add pdfFiller Google Chrome Extension to your web browser to start editing compact modeling in verilog and other documents directly from a Google search page. The service allows you to make changes in your documents when viewing them in Chrome. Create fillable documents and edit existing PDFs from any internet-connected device with pdfFiller.

Fill out your compact modeling in verilog online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Compact Modeling In Verilog is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.