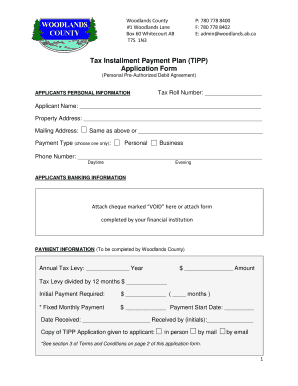

Get the free Dynamic Partial Reconfigurable FPGA

Show details

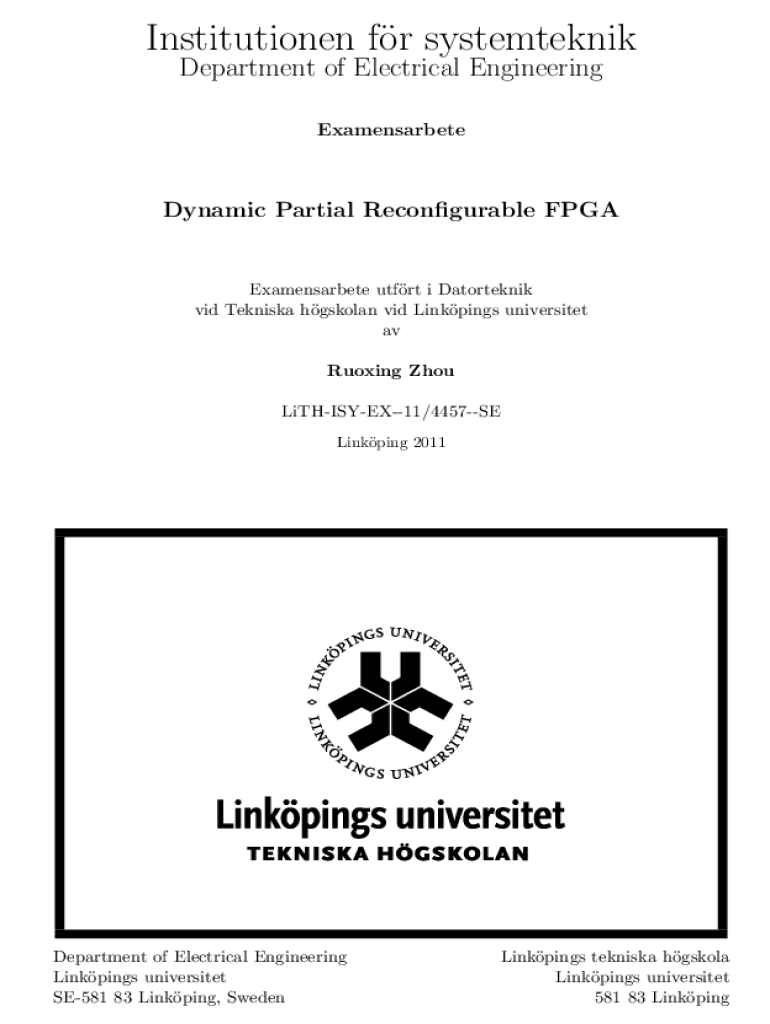

Institutionen fr systemteknik Department of Electrical Engineering ExamensarbeteDynamic Partial Reconfigurable FPGAExamensarbete utfrt i Datorteknik vid Tekniska hgskolan vid Linkpings universitet

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign dynamic partial reconfigurable fpga

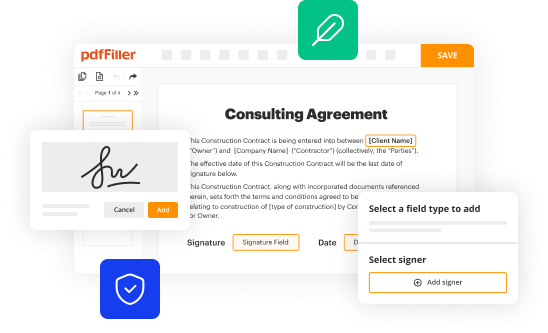

Edit your dynamic partial reconfigurable fpga form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

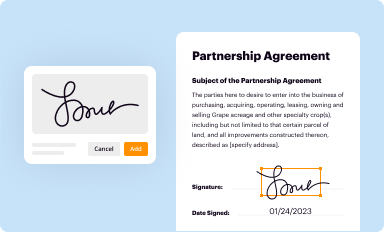

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

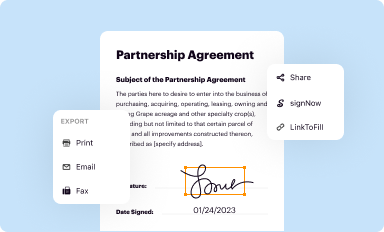

Share your form instantly

Email, fax, or share your dynamic partial reconfigurable fpga form via URL. You can also download, print, or export forms to your preferred cloud storage service.

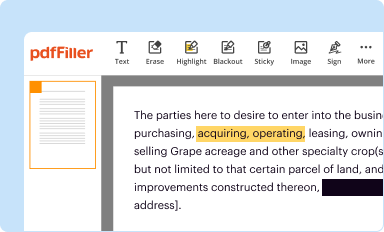

Editing dynamic partial reconfigurable fpga online

To use the services of a skilled PDF editor, follow these steps below:

1

Create an account. Begin by choosing Start Free Trial and, if you are a new user, establish a profile.

2

Simply add a document. Select Add New from your Dashboard and import a file into the system by uploading it from your device or importing it via the cloud, online, or internal mail. Then click Begin editing.

3

Edit dynamic partial reconfigurable fpga. Replace text, adding objects, rearranging pages, and more. Then select the Documents tab to combine, divide, lock or unlock the file.

4

Get your file. Select the name of your file in the docs list and choose your preferred exporting method. You can download it as a PDF, save it in another format, send it by email, or transfer it to the cloud.

With pdfFiller, it's always easy to work with documents. Try it!

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out dynamic partial reconfigurable fpga

How to fill out dynamic partial reconfigurable fpga

01

Identify the design requirements and choose an appropriate FPGA that supports dynamic partial reconfiguration.

02

Set up your development environment with the necessary software tools, such as a hardware description language (HDL) compiler and a synthesis tool.

03

Create a top-level design that includes the modules you intend to reconfigure and those that remain static.

04

Divide the circuit into static and dynamic regions; ensure the interfaces between these regions are well-defined.

05

Implement the dynamic regions as separate FPGA modules, designing them to use a common interface, which allows for seamless reconfiguration.

06

Use a place-and-route tool to map the design, while ensuring that the dynamic regions can be modified without affecting the static regions.

07

Write the necessary control logic to manage the reconfiguration process, which involves loading new configurations into the FPGA.

08

Simulate the design to verify functionality and stability of the statically and dynamically reconfigurable parts.

09

Load the design onto the FPGA and test the dynamic partial reconfiguration by swapping configurations in real-time.

Who needs dynamic partial reconfigurable fpga?

01

Embedded system developers who need to optimize resource usage on hardware.

02

Researchers in fields such as reconfigurable computing and hardware acceleration.

03

Industries that require adaptable hardware solutions, such as telecommunications and automotive.

04

Application developers looking to improve performance for specific tasks by reprogramming hardware on-the-fly.

05

Companies in the defense and aerospace sectors, where changing requirements may demand rapid hardware updates.

Fill

form

: Try Risk Free

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

How do I edit dynamic partial reconfigurable fpga straight from my smartphone?

The pdfFiller mobile applications for iOS and Android are the easiest way to edit documents on the go. You may get them from the Apple Store and Google Play. More info about the applications here. Install and log in to edit dynamic partial reconfigurable fpga.

How do I fill out the dynamic partial reconfigurable fpga form on my smartphone?

Use the pdfFiller mobile app to complete and sign dynamic partial reconfigurable fpga on your mobile device. Visit our web page (https://edit-pdf-ios-android.pdffiller.com/) to learn more about our mobile applications, the capabilities you’ll have access to, and the steps to take to get up and running.

Can I edit dynamic partial reconfigurable fpga on an Android device?

You can edit, sign, and distribute dynamic partial reconfigurable fpga on your mobile device from anywhere using the pdfFiller mobile app for Android; all you need is an internet connection. Download the app and begin streamlining your document workflow from anywhere.

What is dynamic partial reconfigurable fpga?

Dynamic partial reconfigurable FPGA refers to a type of Field Programmable Gate Array (FPGA) that allows certain regions of the chip to be reconfigured while the rest of the FPGA continues to operate. This enables real-time updates and modifications to the hardware without interrupting ongoing processes.

Who is required to file dynamic partial reconfigurable fpga?

Typically, developers and engineers who design systems utilizing dynamic partial reconfigurable FPGAs are required to file necessary documentation to comply with regulatory and technical standards. This may include companies in fields such as telecommunications, aerospace, and automotive where FPGA implementations are used.

How to fill out dynamic partial reconfigurable fpga?

Filling out a dynamic partial reconfigurable FPGA involves several steps including selecting the configuration design, partitioning the FPGA into static and dynamic regions, using suitable design tools to program the dynamic regions, and loading the configuration onto the FPGA during runtime without disrupting active operations.

What is the purpose of dynamic partial reconfigurable fpga?

The purpose of dynamic partial reconfigurable FPGA is to provide flexibility and adaptability in hardware design. It allows for the modification of parts of the FPGA in real-time, enabling it to perform different tasks or adapt to changing requirements without the need for complete reprogramming or downtime.

What information must be reported on dynamic partial reconfigurable fpga?

Information that must be reported on dynamic partial reconfigurable FPGA includes the configuration files, design specifications, performance metrics, reconfiguration methods, and any compliance or regulatory information needed for the application or deployment scenario.

Fill out your dynamic partial reconfigurable fpga online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Dynamic Partial Reconfigurable Fpga is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.