Get the free SmartFusion2/IGLOO2 FPGA Timing Constraints (Enhanced Constraint Flow) User's Guide

Show details

SmartFusion2/IGLOO2 FPGA Timing Constraints for Enhanced Constraints Flow Users Guide For Libero SoC v11.7SmartFusion2/IGLOO2 FPGA Timing Constraints Users Suitable of Contents Introduction. . . .

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign smartfusion2igloo2 fpga timing constraints

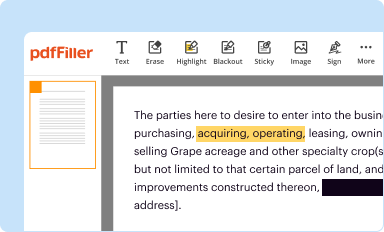

Edit your smartfusion2igloo2 fpga timing constraints form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

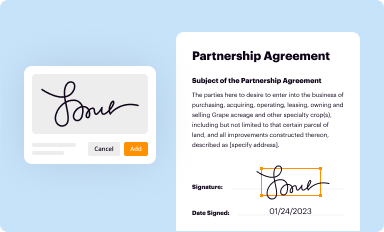

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

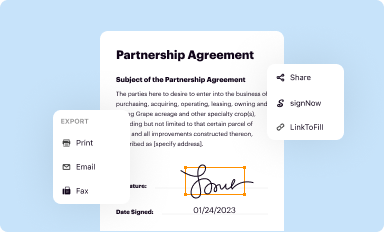

Share your form instantly

Email, fax, or share your smartfusion2igloo2 fpga timing constraints form via URL. You can also download, print, or export forms to your preferred cloud storage service.

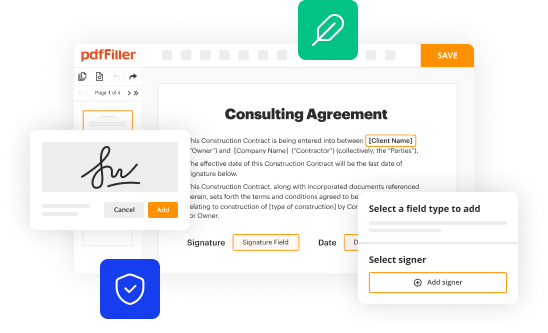

How to edit smartfusion2igloo2 fpga timing constraints online

To use the professional PDF editor, follow these steps:

1

Sign into your account. In case you're new, it's time to start your free trial.

2

Upload a file. Select Add New on your Dashboard and upload a file from your device or import it from the cloud, online, or internal mail. Then click Edit.

3

Edit smartfusion2igloo2 fpga timing constraints. Add and change text, add new objects, move pages, add watermarks and page numbers, and more. Then click Done when you're done editing and go to the Documents tab to merge or split the file. If you want to lock or unlock the file, click the lock or unlock button.

4

Get your file. Select your file from the documents list and pick your export method. You may save it as a PDF, email it, or upload it to the cloud.

The use of pdfFiller makes dealing with documents straightforward. Try it right now!

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out smartfusion2igloo2 fpga timing constraints

How to fill out smartfusion2igloo2 fpga timing constraints

01

Identify the timing constraints required for your design such as clock constraints, input/output delays, etc.

02

Open the Timing Constraints Wizard in Libero SoC and create a new timing constraints file for your project.

03

Add constraints such as clock periods, input/output delay constraints, etc. to the constraints file.

04

Run the timing analysis tool to verify that the constraints are met by your design.

05

Make any necessary adjustments to the constraints file based on the timing analysis results.

06

Once all timing constraints have been properly defined and verified, save the constraints file and include it in your project.

Who needs smartfusion2igloo2 fpga timing constraints?

01

Design engineers working on projects that involve smartfusion2igloo2 fpga devices.

02

Engineers looking to ensure proper timing and performance of their fpga designs.

03

Anyone looking to optimize their fpga designs for better overall performance.

Fill

form

: Try Risk Free

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

How do I execute smartfusion2igloo2 fpga timing constraints online?

Filling out and eSigning smartfusion2igloo2 fpga timing constraints is now simple. The solution allows you to change and reorganize PDF text, add fillable fields, and eSign the document. Start a free trial of pdfFiller, the best document editing solution.

Can I create an eSignature for the smartfusion2igloo2 fpga timing constraints in Gmail?

You can easily create your eSignature with pdfFiller and then eSign your smartfusion2igloo2 fpga timing constraints directly from your inbox with the help of pdfFiller’s add-on for Gmail. Please note that you must register for an account in order to save your signatures and signed documents.

How do I edit smartfusion2igloo2 fpga timing constraints on an iOS device?

Create, modify, and share smartfusion2igloo2 fpga timing constraints using the pdfFiller iOS app. Easy to install from the Apple Store. You may sign up for a free trial and then purchase a membership.

What is smartfusion2igloo2 fpga timing constraints?

SmartFusion2igloo2 FPGA timing constraints are requirements set to ensure the correct operation and performance of the FPGA.

Who is required to file smartfusion2igloo2 fpga timing constraints?

Design engineers or FPGA developers working on projects involving SmartFusion2igloo2 FPGAs are required to file timing constraints.

How to fill out smartfusion2igloo2 fpga timing constraints?

Smartfusion2igloo2 FPGA timing constraints are filled out using tools provided by FPGA synthesis software, specifying the timing requirements for different signals and paths within the design.

What is the purpose of smartfusion2igloo2 fpga timing constraints?

The purpose of SmartFusion2igloo2 FPGA timing constraints is to ensure that the design meets the required performance specifications, such as maximum clock frequency and setup/hold times.

What information must be reported on smartfusion2igloo2 fpga timing constraints?

SmartFusion2igloo2 FPGA timing constraints must report details such as clock frequency, input/output delay requirements, setup/hold times, and any specific timing requirements for critical paths.

Fill out your smartfusion2igloo2 fpga timing constraints online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Smartfusion2Igloo2 Fpga Timing Constraints is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.