Get the free Verilog Description of Combinational Logic

Get, Create, Make and Sign verilog description of combinational

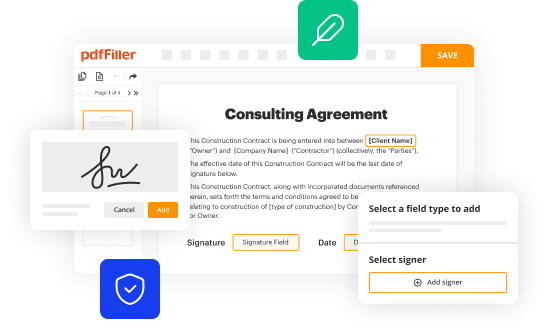

How to edit verilog description of combinational online

Uncompromising security for your PDF editing and eSignature needs

How to fill out verilog description of combinational

How to fill out verilog description of combinational

Who needs verilog description of combinational?

Verilog description of combinational form: A comprehensive guide

Understanding combinational logic in Verilog

Combinational logic refers to circuits where the output is solely dependent on the current inputs, rather than past inputs or states. This means that any change in the input instantly results in a change in the output. Verilog is crucial for describing digital logic circuits because it provides a standardized format for defining hardware implementations, making it easier to visualize and simulate circuit behavior.

The key difference between combinational and sequential logic lies in memory usage. Unlike sequential logic, which relies on storage elements (like flip-flops) to hold state information, combinational logic circuits have no memory and are purely functional. Understanding these distinctions is essential when designing reliable and efficient digital systems, as choosing the right logic model can impact performance and resource usage.

Core concepts of combinational logic in Verilog

Verilog uses a specific syntax to describe combinational logic. Among the basic constructs are the ‘assign’ statements, which help in defining the relationships between inputs and outputs. Additionally, ‘always’ blocks can be used to describe combinational logic as well, providing flexibility in coding and enhancing readability.

Verilog supports two primary data types relevant for combinational logic: ‘wire’ and ‘reg’. A ‘wire’ is typically used to connect different elements of a circuit and can carry values continuously, whereas ‘reg’ holds values only when driven by an ‘always’ block or other procedural statements. Understanding when to use each data type is fundamental for effective circuit design in Verilog.

Writing combinational logic with ‘assign’ statements

Assign statements in Verilog are a simple and effective way to describe combinational logic circuits. The syntax for an assign statement is straightforward, typically following the format: 'assign

For example, by using assign statements, you can easily create a two-input AND gate using the line: 'assign y = a & b;'. Similarly, a four-input OR gate can be represented with: 'assign y = a | b | c | d;'. These representations emphasize how compact and readable Verilog can be for combinational circuits.

Creating complex combinational circuits with always blocks

While assign statements are suitable for simple logic expressions, ‘always’ blocks provide greater complexity in combinational logic design. The basic syntax of an always block is: 'always @* begin ... end'. The '*' indicates that it should react to any changes in its inputs, allowing for dynamic responses.

For example, a half adder can be implemented using an always block. The half adder's outputs are defined as: 'always @* begin sum = a ^ b; carry = a & b; end'. A full adder can be similarly constructed by extending the logic to handle carry input, showcasing how always blocks can be used to create reusable and extensible logic designs.

Implementing multiplexers and demultiplexers

Multiplexers (MUX) and demultiplexers (DEMUX) are essential components in digital logic design. A multiplexer channels multiple inputs into a single output, while a demultiplexer does the reverse, routing a single input to multiple outputs. Implementing these components in Verilog involves understanding their selection logic.

For a 2x1 multiplexer, the Verilog code might be: 'assign y = sel ? b : a;'. Conversely, a 1x4 demultiplexer can be designed using an always block where the selection lines dictate the output according to the input condition. These components are widely used in data routing applications.

Decoders and encoders in combinational logic

Decoders and encoders are crucial in various applications, including memory addressing and data encoding schemes. Decoders convert binary information from 'n' input lines to '2^n' output lines, whereas encoders perform the inverse operation, mapping '2^n' inputs to 'n' output lines. The coding for a 4x16 decoder is structured to expand 4 input lines into 16 distinct output lines, highlighting how encoders and decoders can be efficiently implemented in Verilog.

A 4x16 decoder implementation may use multiple and gates to drive the appropriate output lines, defined in terms of conditions for each possible input combination. Real-world applications for such devices span from memory management systems to complex control logic in processors.

Simulating combinational logic with testbenches

Testbenches are vital to verifying the functionality of combinational logic circuits. They allow designers to simulate input conditions and observe output behavior without the need for physical hardware. Effective testbenches are structured to instantiate the design under test (DUT) and apply a range of input conditions systematically.

When writing a testbench for a full adder, for instance, you would create varied input combinations for A, B, and Cin and observe Sum and Carry outputs accordingly. This enables the identification of potential design flaws early in the development process, thereby reducing errors in physical implementations.

Best practices for describing combinational logic in Verilog

When developing combinational logic circuits in Verilog, best practices can greatly enhance code clarity and maintainability. Using meaningful naming conventions for signals and modules helps others (and your future self) understand the purpose of each component in your design quickly. Keeping consistent formatting and comments throughout the code can make reviewing and troubleshooting more efficient.

Further, thorough testing and validation are essential to ensure that your designs function as expected. Common pitfalls include neglecting to account for all input combinations in testbenches and not revisiting design choices after validating the initial concept. Avoiding these missteps fosters a more robust design.

Advanced techniques in Verilog for combinational logic

Advanced Verilog techniques like parameterized modules enhance code reusability and adaptability, which is particularly beneficial in large designs. Parameterized modules allow designers to create flexible components that can be instantiated with various parameters, fitting different application requirements without needing to rewrite code.

In addition, using functions and tasks can simplify complex combinational logic designs. Functions can return values while tasks can execute procedural code blocks, making your Verilog designs modular and easier to manage. By understanding these advanced techniques, engineers can produce efficient and maintainable code.

Tools and resources for efficient Verilog coding

Effective Verilog coding and management can be significantly enhanced with the right tools. pdfFiller offers a robust platform for managing all types of documentation related to circuit design, including design specs, simulation results, and review notes. Its cloud-based features enable remote access, collaboration, and easy editing of important files.

In addition to documentation management, using interactive tools for testing and simulating your Verilog code can provide immediate feedback and accelerate the design process. Furthermore, leveraging collaborative tools allows teams to share insights and improve designs in real-time, which is paramount in modern engineering environments.

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

How can I manage my verilog description of combinational directly from Gmail?

How can I send verilog description of combinational for eSignature?

How do I make edits in verilog description of combinational without leaving Chrome?

What is verilog description of combinational?

Who is required to file verilog description of combinational?

How to fill out verilog description of combinational?

What is the purpose of verilog description of combinational?

What information must be reported on verilog description of combinational?

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.