Get the free xilinx edk timing constraints form

Show details

Filing Timing Constraints User Guide UG612 (v1.0.0) December 9, 2008, R Filing is disclosing this user guide, manual, release note, and/or specification (the Documentary n”) to you solely for use

We are not affiliated with any brand or entity on this form

Get, Create, Make and Sign xilinx edk timing constraints

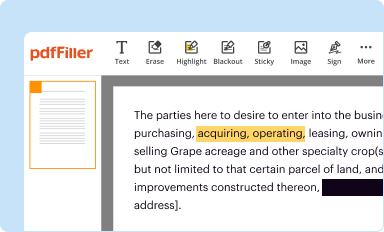

Edit your xilinx edk timing constraints form online

Type text, complete fillable fields, insert images, highlight or blackout data for discretion, add comments, and more.

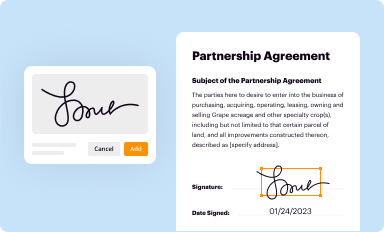

Add your legally-binding signature

Draw or type your signature, upload a signature image, or capture it with your digital camera.

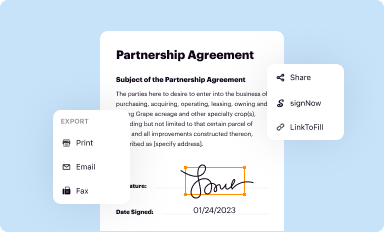

Share your form instantly

Email, fax, or share your xilinx edk timing constraints form via URL. You can also download, print, or export forms to your preferred cloud storage service.

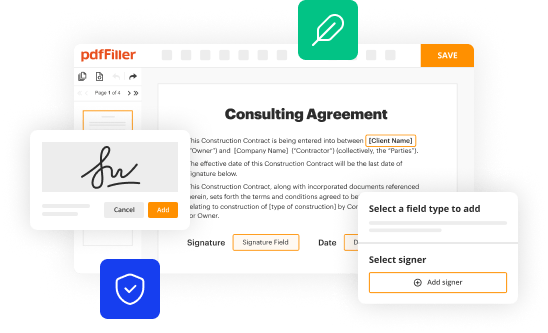

How to edit xilinx edk timing constraints online

To use our professional PDF editor, follow these steps:

1

Create an account. Begin by choosing Start Free Trial and, if you are a new user, establish a profile.

2

Prepare a file. Use the Add New button. Then upload your file to the system from your device, importing it from internal mail, the cloud, or by adding its URL.

3

Edit xilinx edk timing constraints. Add and change text, add new objects, move pages, add watermarks and page numbers, and more. Then click Done when you're done editing and go to the Documents tab to merge or split the file. If you want to lock or unlock the file, click the lock or unlock button.

4

Get your file. Select the name of your file in the docs list and choose your preferred exporting method. You can download it as a PDF, save it in another format, send it by email, or transfer it to the cloud.

It's easier to work with documents with pdfFiller than you can have ever thought. Sign up for a free account to view.

Uncompromising security for your PDF editing and eSignature needs

Your private information is safe with pdfFiller. We employ end-to-end encryption, secure cloud storage, and advanced access control to protect your documents and maintain regulatory compliance.

How to fill out xilinx edk timing constraints

To fill out Xilinx EDK timing constraints, follow these steps:

01

Identify the desired timing requirements for your design. This includes determining the input and output delays that need to be met.

02

Open the Xilinx Platform Studio (XPS) tool and create a new project for your design. This will serve as the basis for filling out the timing constraints.

03

In the XPS tool, navigate to the "Constraints" tab and select the "Timing Constraints" option. This will open the timing constraints editor.

04

Start by specifying the input and output delays for each relevant signal. This can be done by using the "set_input_delay" and "set_output_delay" commands in the timing constraints language (XDC or SDC).

05

Determine the clock signals in your design and define the clock periods using the "create_clock" command. This helps the tool analyze the timing relationships between different signals.

06

If needed, define any clock groups or exceptions using the appropriate timing constraints commands. This is useful when dealing with asynchronous or multicycle paths.

07

Add any other necessary timing constraints, such as constraints related to false paths, require constraints, or clock domain crossings.

08

Verify the correctness of the timing constraints by running a design rule check (DRC) or a timing analysis tool. This ensures that the constraints are valid and consistent with the design.

Who needs Xilinx EDK timing constraints?

01

Designers using Xilinx FPGAs or SoCs that are implementing complex digital designs requiring precise timing control.

02

Engineers working on high-speed or mission-critical systems where meeting timing requirements is vital.

03

Hardware designers involved in integrating IP blocks or peripherals into a larger system, as timing constraints help ensure proper timing between different components.

In summary, filling out Xilinx EDK timing constraints involves specifying input and output delays, defining clock signals and periods, and adding any necessary constraints. These constraints are useful for designers working on complex digital designs, high-speed systems, or integrating IP blocks into larger systems.

Fill

form

: Try Risk Free

For pdfFiller’s FAQs

Below is a list of the most common customer questions. If you can’t find an answer to your question, please don’t hesitate to reach out to us.

How can I get xilinx edk timing constraints?

The premium subscription for pdfFiller provides you with access to an extensive library of fillable forms (over 25M fillable templates) that you can download, fill out, print, and sign. You won’t have any trouble finding state-specific xilinx edk timing constraints and other forms in the library. Find the template you need and customize it using advanced editing functionalities.

How do I complete xilinx edk timing constraints online?

pdfFiller has made filling out and eSigning xilinx edk timing constraints easy. The solution is equipped with a set of features that enable you to edit and rearrange PDF content, add fillable fields, and eSign the document. Start a free trial to explore all the capabilities of pdfFiller, the ultimate document editing solution.

How can I edit xilinx edk timing constraints on a smartphone?

You can do so easily with pdfFiller’s applications for iOS and Android devices, which can be found at the Apple Store and Google Play Store, respectively. Alternatively, you can get the app on our web page: https://edit-pdf-ios-android.pdffiller.com/. Install the application, log in, and start editing xilinx edk timing constraints right away.

What is xilinx edk timing constraints?

Xilinx EDK timing constraints are rules or specifications that define the desired timing behavior of a design implemented using Xilinx Embedded Development Kit (EDK). These constraints ensure that the design meets the required timing requirements and help in achieving optimal performance.

Who is required to file xilinx edk timing constraints?

Designers and developers who are working on Xilinx EDK projects are required to create and file timing constraints for their designs. They are responsible for specifying the timing requirements and ensuring that the design meets these requirements.

How to fill out xilinx edk timing constraints?

To fill out Xilinx EDK timing constraints, designers need to specify various timing parameters such as setup time, hold time, clock frequency, input delay, output delay, etc. These parameters are defined in a constraints file using the appropriate syntax and are associated with specific design elements such as inputs, outputs, clocks, etc. The file is then included in the project and used by the synthesis and implementation tools to enforce the desired timing behavior.

What is the purpose of xilinx edk timing constraints?

The purpose of Xilinx EDK timing constraints is to ensure that the design meets the required timing specifications and achieves optimal performance. These constraints help in preventing timing violations, such as setup and hold violations, by guiding the synthesis and implementation tools to generate a design that meets the timing requirements. They also enable designers to specify the desired timing behavior of their design and control various aspects such as clock frequency, input/output delays, etc.

What information must be reported on xilinx edk timing constraints?

Xilinx EDK timing constraints typically include information such as setup time, hold time, clock frequency, input delay, output delay, etc. These constraints specify the desired timing behavior of the design and provide guidelines for the synthesis and implementation tools to meet the timing requirements. Designers may also include specific constraints for different design elements such as inputs, outputs, clocks, etc., to ensure proper timing behavior.

Fill out your xilinx edk timing constraints online with pdfFiller!

pdfFiller is an end-to-end solution for managing, creating, and editing documents and forms in the cloud. Save time and hassle by preparing your tax forms online.

Xilinx Edk Timing Constraints is not the form you're looking for?Search for another form here.

Relevant keywords

Related Forms

If you believe that this page should be taken down, please follow our DMCA take down process

here

.

This form may include fields for payment information. Data entered in these fields is not covered by PCI DSS compliance.